## The CED Power1401-3A Owners Handbook

Copyright © Cambridge Electronic Design Limited 2016

Neither the whole nor any part of the information contained in, or the product described in, this guide may be adapted or reproduced in any material form except with the prior written approval of Cambridge Electronic Design Limited.

1st edition (1.1) August 2016

## Published by:

Cambridge Electronic Design Limited Science Park Milton Road Cambridge CB4 0FE UK

Telephone: +44 (0)1223 420186

USA & Canada Toll Free: 1-800-345-7794

Fax: +44 (0)1223 420488

Web: www.ced.co.uk

Email: info@ced.co.uk

Trademarks and Tradenames used in this guide are acknowledged to be the Trademarks and Tradenames of their respective Companies and Corporations.

## **Table of contents**

| Preface              | Publishing information                      | i                    |

|----------------------|---------------------------------------------|----------------------|

|                      | Table of contents                           | ii                   |

|                      | Typographic conventions                     | iv                   |

|                      | Use of symbols                              | iv                   |

|                      | Potential for Radio/Television interference | V                    |

|                      | Power1401-3A upgrades                       | vi                   |

|                      | Life support                                | vi                   |

| Getting started      | Fast installation guide                     | 1                    |

| Vith the             | Introduction                                | 2                    |

|                      | C C 1 1 1                                   | 2<br>3               |

| Power1401-3          | Installing the Power1401-3                  |                      |

|                      | Storage and operating environment           |                      |

|                      | Application software                        |                      |

|                      | ripplication software                       |                      |

| Installing the       | Overview                                    | 6                    |

| <b>USB</b> interface | Software installation                       | 6                    |

|                      | Hardware installation                       | 6                    |

| Test software        | Installing test & diagnostics               | 9                    |

|                      | Windows diagnostics                         | 10                   |

| Annlication          | Running the Power1401 with Spike2           | 12                   |

| coftware: Spike?     | Running the Power1401 with Signal           | 13                   |

| & Signal             | Rummig the Fower 1401 with Dightar          | 13                   |

|                      | Ganaral                                     | 1.4                  |

| inputs and           | General                                     | 1 <del>4</del><br>15 |

| outputs              | Waveform output                             | 13<br>17             |

|                      | The rear-panel analogue connector           |                      |

|                      | Clocks                                      |                      |

|                      | Frequency synthesizer                       |                      |

|                      | Event inputs                                |                      |

|                      | Digital input and output                    |                      |

|                      | USB port                                    |                      |

|                      | Synchronization port                        |                      |

|                      | RS232                                       |                      |

|                      | DC power inlet                              |                      |

|                      | De power mice                               | ∠0                   |

## Table of contents

| Hardware         | The ADC16 top-box: 16 waveform inputs              | 29       |

|------------------|----------------------------------------------------|----------|

| expansion        | The PGA16 top-box: 16 programmable-gain ADC inputs | 30       |

| Схранзіон        | The Signal top-box: 4 extra DACs                   |          |

|                  | The Spike2 top-box: digital BNC connections        |          |

|                  |                                                    |          |

| Mechanics of the | Construction                                       | 33       |

| Power1401-34     | Earthing                                           | 34       |

| 1 0 1 0 1 1 0 1  | Upgrade by users                                   | 34       |

| Maintenance      | Introduction                                       | 35       |

|                  | T 11 1 11 00                                       |          |

| operations       | Switch settings                                    |          |

|                  | I/O components                                     |          |

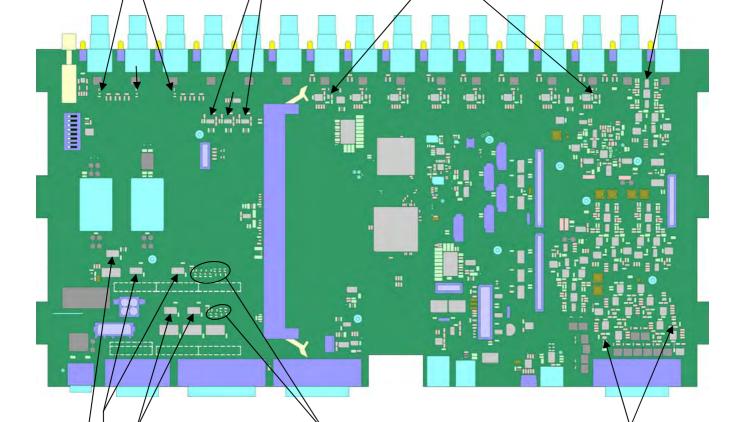

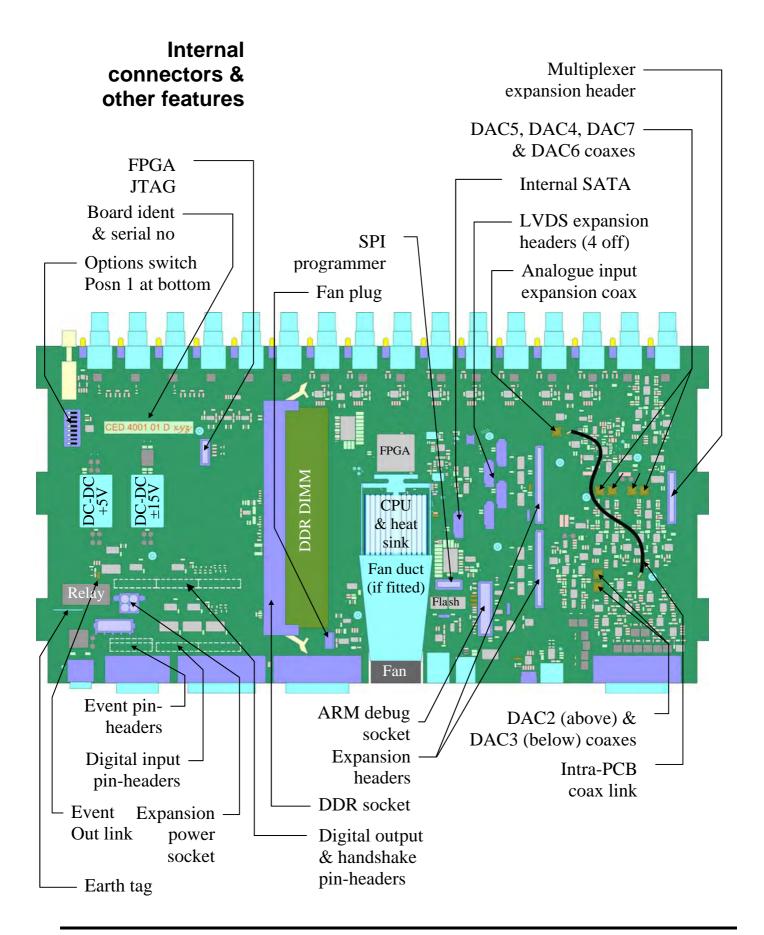

|                  | Internal connectors & other features               |          |

|                  | Memory upgrades                                    |          |

|                  | Setting the ADC input range                        |          |

|                  | Flash ROM                                          |          |

|                  | Analogue calibration                               |          |

|                  | Cleaning the Power1401                             |          |

| Tuankla          | Overview                                           | 12       |

| Trouble          | Overview                                           | 43<br>42 |

| shooting         | Stand-alone test                                   | 43<br>11 |

|                  | LED diagnostic patterns                            |          |

|                  | Calling the CED Help Desk                          | 45       |

| Index            | Index                                              | 1        |

|                  | User notes                                         | 1        |

| Specification    | Specification                                      | 50       |

|                  | FC declaration of conformity                       |          |

## **General information**

# conventions .

**Typographic** The following conventions apply to the text in this manual:

- Ordinary text is in Times New Roman

- Titles of chapters, other manuals and other publications, including CDs, are in Times New Roman italics

- Labels and identifiers appearing on the equipment described in this manual are in Arial

- Menu items, buttons, and other contents of computer displays are in Arial italics

- Names of files, drives, paths and directories are in Courier

- Signal names are in Times New Roman, SMALL CAPS

Use of symbols Where applied, the following symbols have the meanings below:

This symbol declares that the equipment passes the relevant clauses of EU directives on safety and EMC emissions. See the certificate reproduced on page 51

Observe precautions against electrostatic discharge

The CED Power1401-3A is lead-free and conforms to the EU RoHS directive

The CED Power1401-3A is subject to the EU WEEE regulations and may be returned to CED Ltd for recycling

Attention, consult accompanying documents

The DC symbol indicates that the Power1401-3A chassis is powered from a DC-only supply

The earth symbol indicates a metallic contact at mains earth potential

# Potential for Radio/Television Interference (USA only)

The Power1401-3A generates and uses radio frequency energy and may cause interference to radio and television reception. Your Power1401-3A complies with the Specification in Subpart J of Part 15 of the Federal Communications rules for a Class A computing device. These specifications provide reasonable protection against such interference in a residential installation. However there is no guarantee that interference will not occur in a particular installation. If the Power1401-3A does cause interference to radio or television reception, which can be determined by turning the Power1401-3A mains supply off and on, you can try to eliminate the interference problem by doing one or more of the following:

- Re-orient the receiving antenna

- Re-orient the position of the Power1401-3A with respect to the receiver

- Move the Power1401-3A away from the receiver

- Plug the Power1401-3A into a different outlet so that the Power1401-3A and the receiver are on different branch circuits

If necessary, consult CED or an experienced radio/television technician for additional suggestions. You may find the booklet, prepared by the Federal Communications Commission, helpful: *How to Identify and Resolve Radio/TV Interference Problems*. The booklet is available from the US Government Printing Office, Washington DC 20402, Stock no. 004-000-00345-4.

To comply with FCC rules, Part 15 B Class A Computing device, use only shielded interface cables.

Power1401-3A The Power1401-3A is the evolutionary successor to the upgrades Power1401 II and the Power1401-3. Upgrades include:

## From Power1401 II •

- Completely redesigned computational core using Marvell 78100 microprocessor, with provision for dual-core operation using the Marvell 78200 microprocessor

- Processor clock rate increased from 800 MHz to 1 GHz; bus clock rate increased from 66 MHz to 200 MHz

- Maximum internal memory increased from 1 GByte to 2 GByte of DDR RAM; DDR RAM clock rate increased from 200 MHz to 400 MHz

- USB2 port integral to processor permitting a significantly faster data transfer rate (from 27 MByte/sec to 47 MByte/sec to host; from 10 MByte/sec to 45 MByte/sec to Power1401)

- New de-glitched DAC: 1.5 nV.s maximum glitch energy

- DAC offset & gain calibration by software

- From Power1401-3 FPGA upgraded from XC6LSX45 (43,661 equivalent logic cells) to XC7K70T-2-FBG484C (65,690 equivalent logic cells)

- Flash memory implemented as 16 Mbyte SPI NOR flash with main & backup devices

- New 18-bit, 5 Msample.sec<sup>-1</sup> ADC eliminates analogue trimming & simplifies recalibration (user still sees 16 bits)

Life support CED products are not authorized for use as critical components in life support systems without the express written approval of the chairman of the board of directors of CED.

> Life support systems in this context are systems which support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided, can be reasonably expected to result in a significant injury to the user. A critical component in this context is any component of a life support system whose failure to perform can reasonably be expected to cause the failure of the life support system, or to affect its safety or effectiveness.

## Fast installation guide

**Step 1** Install the software first: either your CED application or the CED 1401 installation CD. CED software currently runs on the 32-bit or 64-bit version of Windows XP or later. If you have an earlier version of Windows, it will need to be upgraded

## **Step 2** Set up your hardware:

- Power-up the computer and the Power1401

- Connect the USB data cable. The cable supplied, labelled 'CED', is shielded and guaranteed for full-speed data transfer. Off-the-shelf items MAY WELL NOT WORK

- USB hardware is recognized and correct driver located automatically. On some versions of Windows, the device driver has to be approved by the user, which requires various *OK* boxes to be clicked

For details, see page 6

## **Step 3** Check the installation:

- Run the TRY1401 utility installed with your CED software. Click on *All On* to select all tests, click on *Run Once* to run the tests

- Running the tests should take only a few seconds and give no errors

## **Step 4** Your Power1401 is now ready for use

## **Getting started with the Power1401-3A**

**Introduction** This manual will guide you through the initial check and installation of your Power1401-3A. It introduces you to the external inputs and outputs, and expansion options. It also describes maintenance and diagnostic procedures. Hereafter, your machine is referred-to as the Power1401 except where it differs from the previous model. '1401' used by itself refers to the 1401 family generically. This manual does not cover 1401 programming or the use of application programs with the Power1401.

Windows version Examples of screen dumps and user dialog are mostly taken from Windows 7, with one or two from Windows XP and Windows 10. Details will differ slightly in other versions of Windows, but the operations are all very straightforward and users should not experience any difficulty.

**Checklist** The installation kit for your Power1401 comprises:

- A Power1401, with optional rack-mount kit

- A power brick with attached DC supply cable

- A mains cable for the power-brick suitable for your country

- A USB data cable: this is a high-quality, shielded item

- An installation disk

- This manual

## The power brick The power brick will run

without adjustment on any mains voltage from 100 V to 240 V, 47 Hz - 63 Hz, drawing a maximum of 1.6 A. It has no switch, being controlled simply by plugging in and switching on at the mains socket. A green LED indicates when the brick is powered up.

The front-panel pushswitch actuates a relav inside the Power1401 that switches DC power to the rest of the circuitry. For complete electrical isolation, mains power must be disconnected from the power brick.

The power brick: PowerSolve PSE60-312 shown

**Confidence** Your Power1401 was soak-tested at CED before shipping. To check pass the test, a Power1401 must not generate a single error in at least 96 hours of testing. The next procedure checks that the Power1401 hardware is in the same state as it left the factory.

Ensure that the front-panel DC switch, marked  $\mathbf{O}$ , is off, with the button protruding from the panel. Insert the power-brick output plug into the DC Power In socket. Check that the Mode selector is in position 1. *Do not* connect the USB cable. Switch the Power1401 on. The switch button should light red, while the yellow LEDs flicker. The button should then turn green, while the yellow LEDs continue to flicker. You can now connect the USB cable. If the button flashes red and green, turn to *Trouble shooting* on page 43.

Installing the Once the Power1401 has passed the confidence check, you Power1401 should turn to the section which deals with installation for your computer, starting on page 6. The remainder of this section deals with general topics. The section starting on page 14 describes the signal inputs and outputs. Following sections deal with expansion options, maintenance and troubleshooting.

Storage and The Power1401-3A must be kept in the temperature range of operating -5° to +50° Celsius, at a humidity of less than 95% saturation, environment non-condensing. The Power1401 is suitable for continuous operation. The Power1401 is not protected against ingress of water or dust. There are no hazardous voltages inside the Power1401. The Power1401 complies with relevant EU and USA requirements for electromagnetic interference. The Power1401 can be recycled: please contact CED for further details

**Position** When choosing a permanent position for your Power1401, note that it prefers the same sort of environment as suits the host computer. The Power1401 normally stands on its base, but it will work on its side or upside down, if required.

The fan The Power1401-3A is equipped with a small fan, to expel the heat generated by the microprocessor and FPGA. This runs as necessary, venting to the rear. Be careful not to obstruct it. There should be a clear space at least 150 mm behind the case.

**Over-temperature** If the fan should fail or be obstructed, a temperature sensor state inside the Power1401 will shut off power to the microprocessor. The over-temperature condition is indicated by the LED in the power switch turning off, and the eight ADC LEDs and two DAC LEDs all turning on. If caused by an obstruction, removing it and switching the Power1401 off and on again should restore normal operation.

Over-temperature display: note power LED is off

Application The Power1401 requires application software to run it. Most software customers will run CED application programs for Power1401, such as Signal or Spike2 (see pages 12 and 13), or products supplied by third parties. Alternatively, you may wish to write your own programs, with the help of the 1401 Language support library (downloadable free of charge from the CED Web site: www.ced.co.uk), and your own computer programming manuals.

**Operating platforms** We support the 1401 family (including the Power1401-3A) under Windows XP (service pack 3), Vista, Windows 7. Windows 8, and Windows 10.

Installing CED CED application software such as Spike2 or Signal is installed application software from a CD. The installation program loads the 1401 drivers at the same time. The installation guide with the software will give more detailed instructions.

# programs

Information on Technical information required to use CED application application programs is contained in the software manuals. Technical histories of some of our programs, upgrade information, and in cases downloadable files. mav found www.ced.co.uk.

**Information for** The 1401 language support kit, for users who wish to program programmers their Power1401 from their host computer, includes the 1401 family programming manual for detailed descriptions of the 1401 standard command library. The Power1401 command development kit includes the Power1401 technical manual, which documents the internal structure of the Power1401, and Writing commands for the Power1401 which deals with writing commands in C to run on the Power1401's processor. Use of this kit is only recommended for program developers that are very experienced in writing embedded software.

**Circuit diagrams** Circuit diagrams for the Power1401-3A can be made available for a fee. Purchasers must sign a non-disclosure agreement. Note that the contents of programmable components (e.g. the SPI flash ROM and the FPGA) are *not* available.

## Installing the USB interface

Overview This section describes how to install a Power1401-3A on a Windows PC, communicating via a USB port.

To install the Power1401 you will need:

- A Power1401

- A power brick and mains cable

- The USB data cable supplied by CED

- The CED software application disk

When installing the PC USB interface, the software is installed first, after which the hardware connection is made between the Power1401 and the computer. Installation follows the same procedure for all Windows operating systems.

**Software** The minimum software needed to control a Power1401 is the installation standard 1401 command library and the USB device drivers. These are supplied on the CED 1401 installation software disk, together with test and diagnostic utilities. To install the software, simply insert the CD. Typically it will autorun. If it does not, run setup.exe.

# application software

Installations with If you are installing Spike2 or Signal, the drivers, command library and test utilities are loaded at the same time as the application.

**Hardware** A Power1401 using the USB interface requires a computer with installation a USB2 port and connector. All you have to do is connect the USB data cable between the computer and the Power1401.

> • The USB cable must be a high-quality product, shielded and rated for full speed, such as the one supplied by CED

**Hot plugging** USB hardware is designed for 'hot plugging'. With the software installed, and both computer and Power1401 switched on, connect the USB cable. This causes the computer's USB hardware to recognize the appearance of a new USB device. A message window will briefly announce that Windows has detected a new USB device and is looking for its driver. Since this has already been installed, it will report that it has found the CED 1401 USB software, and disappear.

Device Manager, view devices by type (Windows 7)

Windows 8, & Windows 10

**USB** interface With the driver installed, the Power1401 becomes a recognized settings in Vista, USB device, and the CED 1401 icon will appear in the Device Windows 7, Manager whenever the Power1401 is plugged in and powered up. You can view the 1401 USB settings by selecting

Start, Control Panel, System

Open System by double-clicking, and select Device Manager. This reveals the hardware devices tree. The '1401 interface' icon will be on a node with an arrow  $\triangleright$ , indicating that a device is present. Click on this to display the 'CED 1401 USB interface' icon. Among the tabs revealed when this is opened, the General tab provides overall device status, and allows for enabling/disabling the device. The Settings tab allows you to set the 1401 device number if you have a multi-1401 installation.

Device Manager, view devices by type (Windows XP)

# Windows XP

**USB** interface With the driver installed, the Power1401 becomes a recognized settings in USB device, and the CED 1401 icon will appear in the Device Manager whenever the Power1401 is plugged in and powered up. You can view the 1401 USB settings by selecting

## Start, Control Panel, System

Open System by double-clicking, select the Hardware tab and press the *Device Manager* button. This reveals the hardware devices tree. The '1401 interface' icon will be on a node with a boxed **±**, indicating that a device is present. Click on this to display the 'CED 1401 USB interface' icon. Among the tabs revealed when this is opened, the General tab provides overall device status, and allows for enabling/disabling the device. The Settings tab allows you to set the 1401 device number if you have a multi-1401 installation.

## Installing test & diagnostics

# & diagnostics

Installing test The Power1401-3A installation CD-ROM includes utilities that verify correct installation of your Power1401, assist in recalibrating the analogue system, and diagnose hardware problems. This software is installed automatically at the same time as the driver, when setup. exe is run.

> CED provides you with 1401 support for Windows in a CD. It can also be downloaded from our website, www.ced.co.uk.

To install from CD under any supported operating system:

- Insert the CD

- The installation program should run automatically

- If it does not, select Start, Run, Browse..., open the CD and choose the file setup.exe

- Click on OK and follow the screen instructions

If the 1401 drivers on the CED 1401 installation disk are newer than those on your system, setup.exe will update them.

Location of software You can choose where setup.exe copies the 1401 files. The default destination is c:\1401. In this case, 1401 utilities are copied into the \1401\utils subdirectory. This manual assumes you have accepted that default. \1401 itself is the directory where 1401 commands are installed.

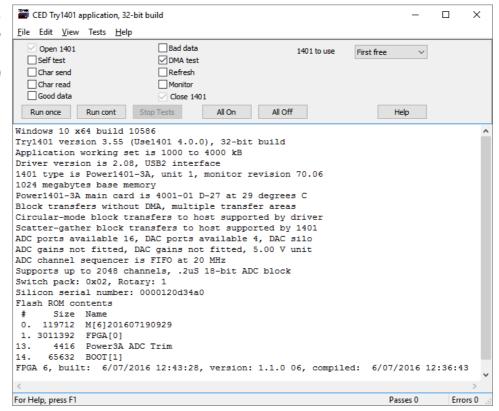

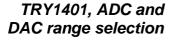

Windows The Windows installation includes the utility TRY1401, that diagnostics verifies that your Power1401 has been installed correctly, and runs diagnostic procedures.

TRY1401

TRY1401 is the principal test program for users. It is also installed as a utility in the program folders of CED applications such as Spike2 and Signal. It simulates a typical 1401 application program and exercises the host computer and Power1401 in the same way.

TRY1401 program screen, displaying 1401 Info... (Windows 10)

The TRY1401 utility is currently installed as the application TRY1432. exe. To run TRY1401, select

## Start, All Programs, 1401 support, TRY1401

Running TRY1401 is self-explanatory. The check boxes allow different aspects of 1401 function to be tested separately. Self test causes the internal self-test hardware to run. Check this if the U LED starts to flash red and green after the Power1401 has been switched on. By clicking Run cont, the selected tests are run continuously, which can be useful for detecting intermittent faults.

**1401 Info...** To access the summary of hardware and firmware information shown on the TRY1401 screen on the previous page, select

File, 1401 Info...

from inside TRY1401.

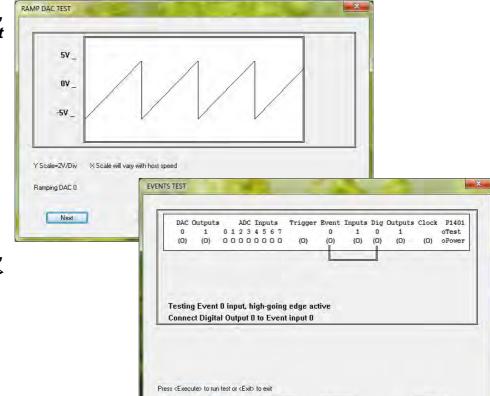

**ADC & DAC Test** If you wish to test or re-calibrate the analogue hardware, or test Event & Clock Test the functions of the Clocks and Events, select

Tests, ADC & DAC Test or Tests, Event & Clock Test

from inside TRY1401. These are tests that the machine cannot do by itself since they require cables to be routed between various connectors, voltages set, &c. The tests are interactive. At each step the user is instructed what equipment is needed, what to do, and what results to expect. Analogue calibration is discussed more fully on page 41.

## ADC & DAC Test, Ramp DAC test

Execute

Repeal Restart

Event & Clock Test. Events test >

Exit

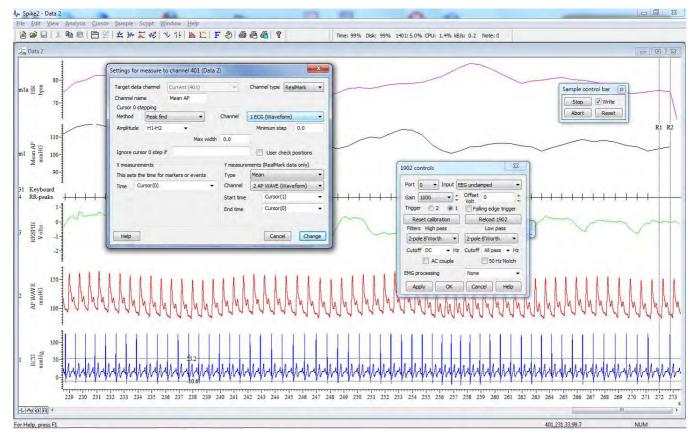

# Spike2

Running the Spike2 is optimized for the analysis and recording of Power1401 with continuous data, possibly on many channels. Analysis of EEGs during sleep, or recording of cardiac output, blood pressure and respiration would be typical tasks. This application example, and the Signal application example below, make use of the CED 1902 isolated pre-amplifier.

Spike2 sampling ECG, with 1902 control panel

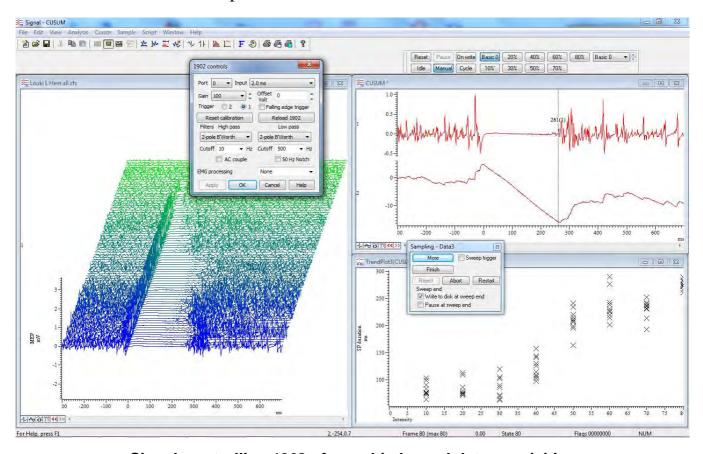

# **Signal**

Running the Signal is optimized for the analysis of sweep based information, Power1401 with where a sequence of data is recorded repetitively, often synchronized to a repeated stimulus. The classic example of this is evoked-response recording: here segments of brain activity are correlated with recurrent stimuli, in order to extract responses buried in the noise.

Signal controlling 1902s for multi-channel data acquisition

**General** The following points deal with physical and electrical aspects of Power1401 connectors, rather than their electronic function.

**Mains earth** The outer sleeves of the front-panel BNCs, and the metal shells of the various rear-panel connectors, are robustly connected to the metalwork of the case and, via the earth pin of the DC inlet and the earth leads of the power brick, to mains earth. All signal returns are tied to mains earth on the printed circuit board. Items of equipment connected to the Power1401 must not be treated as isolated from mains earth, nor from each other.

Front-panel LEDs All front-panel BNCs have adjacent yellow LEDs. These flash or blink as appropriate, e.g. an ADC input LED may light when its channel is active. A DAC output LED may flash when its channel is updated. Digital output LEDs light when their bit is set. LEDs may light to prompt users to make connections. LEDs flash in a distinctive manner on self test. If all ADC and DAC LEDs turn on at once, and the  $\circlearrowleft$  pushbutton LED turns off, this indicates the Power1401 is overheating. The pushbutton lights red to indicate self-test, and flashes red and green if a hardware error has been detected. Normally it glows green, indicating that none of the internal voltage rails has drifted outside limits. See also *LED diagnostic patterns*, page 44.

## Externallyconnected chips

ICs connected directly to the outside world are susceptible to damage from electrostatic discharge or signal overload, though in practice this seems to happen only rarely. ADC inputs and DAC outputs are diode-clamped to ±15 V. Digital-output ICs are diode-clamped to +5 V and ground. Digital-input and eventinput signals are protected by MOSFET devices and are safe against moderate overvoltages of either polarity. However, if these measures fail, damaged ICs must be unsoldered and replaced. All such ICs are readily-available types. If ordering, specify the exact part-code as on page 36 to ensure lead-free parts. See page 35 for opening the Power1401 and page 36 for the location and identification of I/O chips. See page 45 for sending the 1401 back to CED.

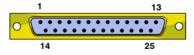

Connector diagrams On the following pages, all rear-panel connectors are drawn as the user sees them, i.e. viewed from the outside. This is also the view of their mating connectors as seen while wiring them up!

Waveform input There are sixteen waveform input channels on a standard Power1401. Eight channels are available through front-panel BNC connectors, labelled ADC Inputs, and eight through the rear-panel Analogue Expansion D-socket. All inputs pass through ferrite chokes that block high-frequency noise. The working input range of the ADC (and the DAC outputs) is  $\pm 5$  V or  $\pm 10 \text{ V}$ , as selected in the TRY1401 utility. The choice is retained in the SPI flash memory and is unaffected by power cycling. See page 39 for setting the ADC input range.

Waveform Waveform input channels are buffered through amplifiers. If buffering & gain the programmable-gain option is fitted, the amplifier gains are individually software-settable to unity,  $\times 2$ ,  $\times 5$  or  $\times 10$ . Channels are then steered into the ADC (Analogue to Digital Converter) via multiplexers. The ADC can convert an input signal to a 16bit digital value at up to 3 MHz in single-channel mode, 1 MHz if switching channels. Sampling is inherently sequential; two channels cannot be sampled simultaneously.

## Trigger

The front-panel input labelled Trigger can be set by software to be the external signal to start the clock that controls ADC conversions. When operating in internally-triggered mode the ADC typically samples at a fixed rate set by one of the clocks.

**External convert** The ADC external convert input is also permanently wired through pin 6 of the rear panel Events D-socket. Conversions are usually initiated by a high-to-low transition. External convert signals are used when the conversion time is determined by an external event, e.g. when synchronizing conversions to the phases of a rotating machine.

ADC LEDs The front-panel waveform input channels each have an associated yellow LED. They are controlled by software command and typically turn on when the channel is in use.

Trigger LED

The trigger-input LED flashes or blinks on detection of an active-edge transition at the Trigger input. The LED can be set by software to be either on or off in the quiescent state.

**Technical details:** The input impedance of the waveform channels is 1 megohm. Analogue input The waveform inputs should be driven from a low-impedance source (100 ohms or less): the output of most amplifiers is suitable. The maximum non-destructive input voltage range is ±15 V. If you do overdrive the inputs, the input buffer amplifiers may be damaged. Replacing them requires soldering quite small devices; see page 35 for opening the Power1401, and page 36 for the exact part number to ensure lead-free parts. See page 45 for sending the unit back to CED.

**Front-panel** The front-panel Trigger input has a working voltage range of Trigger input 0 V to +5 V. MOSFET circuit protection allows a safe input range of  $\pm 10$  V. This input is pulled up to +5 V by a 100 kilohm resistor and has input hysteresis: the low-going threshold voltage is 0.95 V and the high-going threshold is 1.2 V. Pulses driving the trigger input should be 1 µs or longer. To pull this input low, the driving device must be able to sink 50 µA.

input

Rear-panel ADC The rear-panel ADC external-convert input is on pin 6 of the external convert Events D-socket. It responds to TTL and switch closure signals, and has a working voltage range of 0 V to +5 V. MOSFET circuit protection allows a safe input range of ±10 V. This input is pulled up to +5 V by a 10 kilohm resistor. Input pulses should be at least 1 µs long and must fall below 0.8 V for guaranteed recognition. Conversion is normally initiated on the high-to-low edge. Use of the rising edge can be selected by switch; see page 35.

The ADC and the FPGA firmware resolve the analogue input voltage into 65536 levels (sixteen-bit precision). Each step is 150  $\mu$ V approximately at  $\pm 5$  V input range, or 300  $\mu$ V at  $\pm 10$  V. The ADC has eighteen-bit resolution, but the extra bits are used to simplify calibration of the analogue input.

Waveform output There are four, and optionally eight, waveform output channels on the Power1401. Two are on front-panel BNC connectors, labelled DAC Outputs (Digital to Analogue Converters), and two on the rear-panel Analogue Expansion DD-socket. If extra DACs have been fitted, their outputs may also be routed on the PCB to the rear panel DD-socket, or else routed by internal coax cables to BNC socket outputs on an expansion top-box. All outputs pass through ferrite chokes that block highfrequency noise.

## range

Analogue voltage The DAC waveform outputs generate voltages in the range  $\pm 5$  V, in steps of approximately 150  $\mu$ V (16-bit precision). The output range may be changed to  $\pm 10 \text{ V}$ , and  $300 \,\mu\text{V}$  steps, by software option. The selected range applies to all four (or eight) DACs and also the ADC inputs. The setting is retained in nonvolatile SPI flash, unaffected by power cycling. See page 39 for setting the DAC output range.

## **Update modes**

The DACs can be programmed to update in response to an external signal, either the rear-panel Event Clock F input (see page 22), or the front panel Trigger input, so as to synchronize the update rate with external equipment. Alternatively, they can be updated at a fixed rate set by one of the internal clocks. When outputting multiple channels of waveform, Power1401 can be programmed to update several DACs simultaneously. The maximum update rate is 500 kHz.

DAC LEDs The front-panel DAC output channels each have an associated yellow LED. The LED is controlled by software and typically turns on when the channel is in use.

**Technical details** The waveform outputs expect to drive loads of 600 ohms' impedance or more, and are short-circuit proof. For full accuracy, the load should be at least 5 kilohms. If an output amplifier is damaged it must be unsoldered and replaced. See page 35 for opening the Power1401. See page 36 for the exact part number to ensure lead-free parts. See page 45 for sending the machine back to CED.

# connector

The rear-panel The rear-panel analogue connector is a 44-way high-density analogue DD-socket. On an unexpanded, four-DAC Power1401 it accommodates ADC input channels 8 - 15 and DAC channels 2 and 3. (For rear-panel channel numbering on expanded units, see below.) The ten signals are on the bottom row of the D-socket, and each has its own ground return on the top row. This is convenient when wiring-up the mating plug with twisted pairs or coaxial cables. The middle row is unconnected, unless the four extra DACs, DAC channels 4 - 7, have been fitted and routed to the rear panel. All signals and returns pass through ferrite chokes that block high-frequency noise.

## numbering

**Rear-panel channel** The rear-panel ADC inputs are defined always to be the last eight channels available. So, if a sixteen-channel ADC expansion top-box is fitted, its channels become 16 - 23 and the rear-panel inputs become ADC channels 24 - 31; if a Spike2 top-box is fitted, with eight ADC channels, the rear-panel inputs become channels 16 - 23.

> The rear-panel DAC outputs are similarly defined to be the last pair (or more) in use. So, if the Signal top-box is fitted, its DACs become 2 - 5, and the rear-panel DACs become 6 and 7; were the four extra DACs also fitted to the motherboard, they would become 8 - 11.

# Rear-panel analogue socket

| Pin     | Function       | Pin    | Function                    |

|---------|----------------|--------|-----------------------------|

| 1, 2    | No connection  | 27     | DAC 6 output *              |

| 3       | ADC 8 return   | 28     | DAC 6 return *              |

| 4       | ADC 9 return   | 29     | DAC 7 output *              |

| 5       | ADC 10 return  | 30     | DAC 7 return *              |

| 6       | ADC 11 return  | 31, 32 | No connection               |

| 7       | ADC 12 return  | 33     | ADC 8 input                 |

| 8       | ADC 13 return  | 34     | ADC 9 input                 |

| 9       | ADC 14 return  | 35     | ADC 10 input                |

| 10      | ADC 15 return  | 36     | ADC 11 input                |

| 11, 12  | No connection  | 37     | ADC 12 input                |

| 13      | DAC 2 return   | 38     | ADC 13 input                |

| 14      | DAC 3 return   | 39     | ADC 14 input                |

| 15      | No connection  | 40     | ADC 15 input                |

| 16 - 22 | No connection  | 41, 42 | No connection               |

| 23      | DAC 4 output * | 43     | DAC 2 output                |

| 24      | DAC 4 return * | 44     | DAC 3 output                |

| 25      | DAC 5 output * |        |                             |

| 26      | DAC 5 return * | Shell  | Mains earth to cable screen |

<sup>\*</sup> These signals are present if the relevant DACs have been fitted and connected to the rear-panel analogue socket, otherwise the pins are no connection.

A suitable mating D-plug, with solder-bucket terminations, is ITW McMurdo part-number HDB44PTD. A suitable shroud is also required.

**Clocks** The Power1401 has five clocks, used for timing and counting external pulses (clocks 0 and 1), generating general-purpose timing pulses (clock 2), controlling waveform output (clocks 3 and 4) and controlling the waveform input sampling rate (clock 4). These clocks are managed automatically by the application software.

**Trigger** You may need to drive a clock from an experiment, e.g. to trigger sweeps of waveform sampling. The front-panel Trigger input will be routed by software to the correct clock, to set it running on your signal.

**Clock output** You may require the application to generate pulses to drive an experiment. The output of Clock 2 is available from the front-panel Clock BNC connector. Frequencies between 10 MHz and 3.55 nHz (one pulse in 8.9 years!) can be generated. The application manual describes this where it is relevant.

Clock inputs Where external signal pulses are to be timed or counted, the application program may use the front-panel Event 0 and Event 1 inputs. Pulses must be 1 µs or wider. If there are more than two such signals, the rear-panel Digital Inputs may be used; see page 26.

Frequency sources All clock frequencies are normally derived from an internal crystal oscillator. Users may sometimes require a timing source from outside the Power1401 instead. All clocks can be driven from an external frequency source via the Clock F input, pin 7 on the rear-panel Events D-socket (see page 22). When you need to synchronize two 1401 machines, use the synchronization port (see page 27).

LEDs The trigger and event-input LEDs flash or blink on detection of an active-edge transition. They can be either off or on in the quiescent state, as set by software, the latter to show that the input is armed and ready to be used. The Clock output LED simply indicates that Clock 2 is running, turning on whenever Clock 2 is enabled.

Frequency The frequency synthesizer is an internal device capable of synthesizer generating frequencies that cannot be obtained by simple integer division of the 25 MHz crystal oscillator. An example of this would be the 44.1 kHz sampling frequency widely used in digital audio applications. Two such frequencies can be generated independently by the frequency synthesizer. The outputs may be used internally, e.g. to control ADC sampling rate or DAC update rate, or routed to the Clock 2 output.

> The frequency synthesizer is not currently (August 2016) supported in application software.

Technical details The normal input range of Trigger, Event 0 and Event 1 is 0 V to +5 V. There is MOSFET circuit protection allowing a safe input range of  $\pm 10$  V. These inputs are held internally to +5 V by 100 kilohm resistors and have input hysteresis: the lowgoing threshold voltage is set at 0.95 V and the high-going threshold at 1.2 V. To pull these inputs low, the driving device must be able to sink 50 µA. Pulses driving these front panel inputs must be 1 µs or wider.

Clock is an output, driven by an SN74LVC1T45DRL lead-free, surface-mount bus driver element which can source or sink 24 mA. Note that, since this is an output device, it cannot have MOSFET protection. If it is damaged, its replacement will involve unsoldering and resoldering. This is a very small device, less than 2 mm square.

Trigger, Clock 2, Event 0, and Event 1 all pass through ferrite chokes that block high-frequency noise.

Event inputs More clock-related inputs, the Clock E series, are provided on the rear-panel Events D-socket. These allow close control of the clocks for 1401 programmers. Full details are given in the 1401 family programming manual, and the Power1401-3A technical manual. The front-panel BNCs Event 0 and Event 1 are often routed by software to the Clock E0 and E1 inputs.

**Technical details** Clock E and Clock F inputs respond to TTL or switch closure signals, and are pulled up to +5 V by 10 kilohm resistors. To pull these inputs low, a driving device must sink at least 500 µA; to guarantee recognition, input pulses must fall below 0.8 V. Clock E pulses must be at least 100 ns wide. Clock F frequency must not exceed 10 MHz; pulses should be 50 ns or wider. The working range of these inputs is 0 V to +5 V. MOSFET circuit protection allows a safe input range of  $\pm 10 \text{ V}$ .

> The sense of the Clock E and ADC external convert inputs may be inverted by a switch option, see page 35, but the inputs would all then be held active high if no input is connected.

**Event Out** The Event Out output is buffered by an SN74LVC1T45DRL single-gate, lead-free, surface-mount buffer that can source or sink 24 mA. Since this is an output device it cannot have MOSFET protection. If it is damaged, its replacement will involve resoldering. Event Out is normally isolated from the rear-panel socket and a motherboard jumper must be inserted to make it available (see page 37). This is to help reduce EMI.

## **Events socket**

| Pin    | Function       | Pin   | Function                     |

|--------|----------------|-------|------------------------------|

| 1      | Clock E0 input | 5     | Clock E4 input               |

| 2      | Clock E1 input | 6     | ADC external convert input   |

| 3      | Clock E2 input | 7     | Clock F input for all clocks |

| 4      | Clock E3 input | 8     | Event Out output             |

| 9 - 15 | Ground         | Shell | Mains earth to cable screen  |

The mating D-plug, with solder-bucket terminations, is ITW McMurdo part-number DA15P. A shroud is also required.

Digital input and The Power1401 has full, sixteen-bit digital I/O available on the output rear-panel D-connectors Digital Inputs and Digital Outputs. Bits may be read or written singly, by low or high byte, or by the whole word.

**Front-panel BNCs** The front-panel Event Inputs can be fed into bits 0 and 1 of the high byte and/or the low byte of the digital inputs if enabled by software. Bits 0 and 1 of the high byte of the digital output are also routed to the front-panel Digital Outputs.

> The input high byte can be programmed for detection and timing of change of state (i.e. any bit changing either way). Digital output can be gated with clock 2 so that it updates on clock 2 ticks. Digital output is normally permanently enabled, but either or both bytes can be turned tristate-off by grounding pin 11 of the output socket, if this has been enabled by software. These bytes are re-enabled whenever pin 11 is high or disconnected.

Digital I/O LEDs Front-panel event-input LEDs flash or blink on detection of active-edge transitions, the quiescent state being set by software command. Front-panel digital-output LEDs simply reflect the state of the bits, being lit whenever their bit is set (high).

**The 1-Wire port** The Power1401-3A is provided with a 1-Wire port on pin 22 of the input connector. This allows bidirectional communication down a single wire (plus ground) to one or more devices, which are also powered from the same wire. Devices currently available include temperature and humidity sensors, as well as 'silicon serial numbers'.

> The 1-Wire port is not currently (August 2016) supported in application software.

## handshake protocol

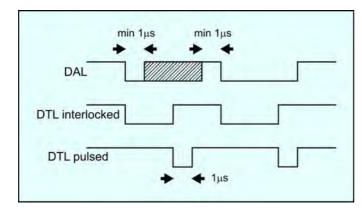

Digital I/O Digital data transfer between the Power1401 and external equipment can optionally be synchronized by pairs of handshake signals. There are separate pairs for each byte. The polarities of all signals can be set independently by software. The example that follows is typical.

When presenting data, an external device sends a pulse at least 1 µs the DAL input wide to (data available. 0 - 7). When the Power1401 reads the data the DTL output line (data transmitted, 0 - 7) pulses for 1 µs if in pulsed mode. If in interlocked mode, DTL is set by the Power1401 read and cleared by the next DAL.

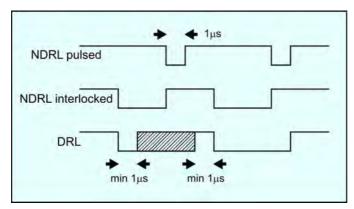

When Power1401 writes data to the digital output, the NDRL output (new data ready, 0 - 7) pulses for 1 µs if in pulsed mode. If in interlocked mode NDRL is set by the data write and cleared by the answering DRL pulse (data read, 0 - 7), at least 1 µs wide, from the external device.

## circuit breaker

**5 volt output and** There is a +5 V output available on pin 25 of both the digital input and output ports. This output is internally protected by a 200 mA circuit-breaker and is intended only to power one or two chips for interfacing purposes. The circuit-breaker is reset by removing power from the Power1401.

> We have occasionally had problems with users who trip this protection very regularly. This is usually caused by a connector with a metal shroud being plugged into the digital input crookedly and the shroud shorting to pin 25, which causes overload. If you have this problem, the simple solution is to make this connection with Power1401 switched off, or to use a connector with a plastic shroud.

**Technical details** All digital inputs have MOSFET circuit protection. All outputs through SN74LVC8T245PW buffered octal. SN74LVC1T45DRL single-gate, lead-free, surface-mount devices, which can source or sink 24 mA. Note that, since these are output devices, they cannot have MOSFET protection. If any are damaged, their replacement will involve unsoldering and resoldering. The single-gate devices are very small, less than 2 mm square.

> Unconnected digital inputs read 1, being pulled internally to +5 V by 4.7 kilohms (at the rear panel) or 100 kilohms (at the front panel). Input voltages of more than 2.0 V will always read as a logic 1. To appear as a logic 0, the input must be pulled down below 0.8 V for at least 1 µs, requiring approximately 50 μA, at the front panel; or 100 ns, requiring approximately 1 mA, at the rear panel.

> On the front panel, Digital In 0 and Digital In 1, Digital Out 0 and Digital Out 1 all pass through ferrite chokes that block high-frequency noise.

# Digital I/O connectors

## **Digital Input plug**

## **Digital Output socket**

| Б.    |                                  | D:    |                             |

|-------|----------------------------------|-------|-----------------------------|

| Pin   | Output function                  | Pin   | Input function              |

|       | High byte out Word out           |       | High byte in Word in        |

| 1     | 7 15                             | 1     | 7 15                        |

| 14    | 6 14                             | 14    | 6 14                        |

| 2     | 5 13                             | 2     | 5 13                        |

| 15    | 4 12                             | 15    | 4 12                        |

| 3     | 3 11                             | 3     | 3 11                        |

| 16    | 2 10                             | 16    | 2 10                        |

| 4     | 1 9                              | 4     | 1 9                         |

| 17    | 0 8                              | 17    | 0 8                         |

|       | Low byte out Word out            |       | Low byte in Word in         |

| 5     | 7 7                              | 5     | 7 7                         |

| 18    | 6 6                              | 18    | 6 6                         |

| 6     | 5 5                              | 6     | 5 5                         |

| 19    | 4 4                              | 19    | 4 4                         |

| 7     | 3 3                              | 7     | 3 3                         |

| 20    | 2 2                              | 20    | 2 2                         |

| 8     | 1 1                              | 8     | 1 1                         |

| 21    | 0 0                              | 21    | 0 0                         |

|       | DRH                              |       | DTH                         |

| 9     | Data received 8-15 i/p           | 9     | Data transmitted 8-15 o/p   |

| 22    | User i/p                         | 2.2   |                             |

| 22    | (buffered, reserved)             | 22    | 1-wire port i/o             |

| 10    | User o/p<br>(buffered, reserved) | 10    | Not connected               |

|       | NDRL                             |       | DAL                         |

| 23    | New data ready 0-7 o/p           | 23    | Data available 0-7 i/p      |

| 11    | Output disable i/p               | 11    | Not connected               |

|       | DRL                              |       | DTL                         |

| 24    | Data received 0-7 i/p            | 24    | Data transmitted 0-7 o/p    |

| 10    | NDRH                             | 10    | DAH<br>Day 11.11 0.15       |

| 12    | New data ready 8-15 o/p          | 12    | Data available 8-15 i/p     |

| 25    | +5V (200mA maximum)              | 25    | +5V (200mA maximum)         |

| 13    | Ground                           | 13    | Ground                      |

| Shell | Mains earth to cable screen      | Shell | Mains earth to cable screen |

The mating connectors, with solder-bucket terminations, are ITW McMurdo part-numbers DB25P (25-way plug) and DB25S (25-way socket). Suitable shrouds are also required.

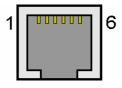

**USB port** The USB port is used to connect the Power1401 to the PC. Both USB1 and USB2 standards are supported. Data transfer rates can reach approximately 38 MBytes/sec for USB2.

> The USB port is a style B socket on the rear panel. USB\_DATA+ and USB DATA- transmit the serial data as a differential pair.

## **USB** socket

| Pin   | Function             |

|-------|----------------------|

| 1     | USB +5V              |

|       | (USB cable detect)   |

| 2     | USB_DATA+            |

| 3     | USB_DATA-            |

| 4     | USB_GND              |

|       | (to system ground)   |

| Shell | Mains earth to cable |

|       | screen               |

connected to USB GND is system ground via a choke. USB\_+5V is used as a cable sense input, also via a choke. applied to this pin indicates that the USB cable is inserted. The Power1401 is specified to meet European and US EMC regulations only if used with braid-screened cables supplied by CED.

**Synchronization** The synchronization port enables two or more 1401s to be port synchronized (Power-3A, Power-3, Power II, micro mk II or Power serial no. P 3xxx onwards, in any mix), so that there is absolutely no drift in timing between units.

The Sync socket is an RJ11 connector with 6 pins loaded. A

## Sync socket

| Pin   | Function             |

|-------|----------------------|

| 1     | MHZ20_TRX-           |

| 2     | MHZ20_IN-            |

| 3     | MHZ20_IN+            |

| 4     | MHZ20_OUT-           |

| 5     | MHZ20_OUT+           |

| 6     | MHZ20_TRX+           |

| Shell | Mains earth to cable |

|       | screen               |

cable screened is chained from unit to unit, with the 'master' end of the cable determining which provides the clock frequency. Up to three 1401s may be synchronized with the master. The units need to be in close physical proximity, either side by side or stacked.

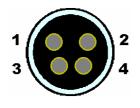

**RS232**

## 8-way mini-DIN

| Pin   | Function             |

|-------|----------------------|

| 1     | CON_DTR              |

| 2     | CON_CTS              |

| 3     | CON_RX               |

| 4     | Ground               |

| 5     | CON_TX               |

| 6,7   | No connection        |

| 8     | Ground               |

| Shell | Mains earth to cable |

|       | screen               |

The RS232 port is only used during the initial setup and for debugging. Under working conditions the Power1401 cannot be programmed via RS232 so this port is not available for users. Its pinout is given here only for the sake of completeness.

**DC power inlet** The external power brick is a switch-mode mains power supply that provides a nominal 12 V DC. This is converted to the required voltage rails inside the Power1401. The internal convertors will accept voltages in the range +9 V to +18 V, so the Power1401 will run off a car battery, for example.

> An internal relay controlled by the front-panel pushbutton switches both +12 V and 0 V. When inserting the DC supply plug, initial contact is made by mains earth when the sleeve engages the DC inlet screen. Mains earth also makes contact via a pin at the same time as the +12 V and 0 V pins.

## DC power socket

| Pin   | Function             |

|-------|----------------------|

| 1     | +12 V                |

| 2     | 0 V                  |

| 3     | SPARE                |

| 4     | Mains earth          |

| Shell | Mains earth to cable |

|       | screen               |

The unexpanded Power1401 will consume approximately 1.3 A at 12 V. This can rise to up to 2.8 A if the Power1401 is fitted with top-boxes.

## Hardware expansion

## top-box: 16 waveform inputs

The ADC16 You may increase the number of waveform inputs by adding the ADC16 expansion top-box with sixteen extra channels, which are mapped onto ADC channels 8 - 23. The rear-panel ADC inputs are then mapped onto channels 24 - 31. Once the Power1401 has been told about the extra channels by the TRY1401 utility, the new ones may be freely used just like the basic set. Software that attempts to read the extra channels will return undefined data values if the ADC16 is not installed.

> Two ADC16s may be added to a Power1401, in which case the second maps onto channels 24 - 39 and the rear-panel ADC inputs map onto channels 40 - 47.

> The ADC inputs on the ADC16 are of identical design to the ones on the main board, with optional selectable gains of unity,  $\times 2$ ,  $\times 5$  or  $\times 10$ . The input range will be  $\pm 5$  V or  $\pm 10$  V as set on the motherboard using TRY1401 (see page 39). The top-box makes internal connections to the Power1401 motherboard. the CED 4001-03, This expansion board. requires Power1401 expanded mechanics (can and case). It is usually more convenient to send an unexpanded unit back to CED for upgrading than for the end-user to install the expansion unit.

# programmablegain ADC inputs

The PGA16 Like the ADC16, the PGA16 top-box provides sixteen more top-box: 16 ADC input channels mapped onto channels 8 - 23 (and the rearpanel ADC inputs onto 24 - 31). In this case, however, each channel has two stages of individually-programmable gain. Typically the first stage will have gains of unity,  $\times 2$ ,  $\times 5$  and  $\times 10$ , and the second stage gains of unity,  $\times 10$  and  $\times 100$ . In this way gains of up to ×1000 are achievable.

> Two PGA16s may be added to a Power1401, in which case the second maps onto channels 24 - 39 and the rear-panel ADC inputs map onto channels 40 - 47.

> The ADC inputs are of similar design to the ones on the main unit, only with two cascaded gain stages. The input range will be  $\pm 5$  V or  $\pm 10$  V as set for the motherboard using TRY1401 (see page 39). The top-box makes internal connections to the Power1401 motherboard. This expansion CED 2701-04, requires the Power1401 expanded mechanics (can and case) and it is usually more convenient to send an unexpanded unit back to CED for upgrading than for the enduser to install it.

## top-box: 4 extra DACs

The Signal The Signal top-box is designed for customers that require a larger number of DACs than usual. It provides another four, are mapped onto DAC output channels 2-5. which Additionally, the two rear-panel DACs on the Power-3A main board are brought out to BNCs on the top-box. Thus there are eight DACs in total, all available from front-panel BNCs.

> The Signal top-box also provides eight channels of ADC input, mapped as channels 8 - 15. The inputs are of identical design to the ones on the main unit, with optional selectable gains of unity,  $\times 2$ ,  $\times 5$  or  $\times 10$ , and input range of  $\pm 5$  V or  $\pm 10$  V as set on the motherboard. The rear-panel ADC inputs are mapped onto channels 16 - 23.

> The top-box also brings two more bits of digital output, bits 2 and 3 of the upper byte, to front-panel BNCs.

> The top-box makes internal connections to the Power1401 motherboard. This expansion board, the CED 2701-05, requires the Power1401 expanded mechanics (can and case), and it is usually more convenient to send an unexpanded unit back to CED for upgrading than for the end-user to install it.

# digital BNC connections

The Spike2 In some circumstances, such as in many Spike2 applications, top-box: the digital inputs and outputs are heavily used for signals. It is convenient to have more of these connectors available on the front panel as BNCs. The Spike2 top-box provides six event inputs, mapped onto bits 2 - 7 of the digital inputs high-byte.

> This expansion board also provides eight ADC inputs mapped onto ADC 8 - 15, of identical design to the ones on the main unit, with optional selectable gains of unity,  $\times 2$ ,  $\times 5$  or  $\times 10$ , and input range of  $\pm 5$  V or  $\pm 10$  V as set on the motherboard. Finally there is a pair of DACs mapped onto DAC 2 - 3.

> When this card is installed, the rear-panel ADC inputs are mapped onto channels 16 - 23, and the rear-panel DACs onto channels 4 and 5.

> The normal input voltage range of the digital inputs is 0 V to +5 V. The safe range is  $\pm 10$  V, and they present an impedance of 100 kilohm, as with the front-panel Event and Trigger inputs. The top-box makes internal connections to the Power1401 motherboard. The expansion board, the CED 2701-09, requires the Power1401 expanded mechanics (can and case) and it is usually more convenient to send an unexpanded unit back to CED for upgrading than for the end-user to install it.

**Construction** The Power1401-3A, like all its predecessors, is built on a single circuit board, the 'motherboard'. This can accept up to two 'daughterboards' as expansion. Daughterboards are bolted to the motherboard on pillars that space the cards 1 U (134" or 44.45 mm) apart, a 'U' being the unit vertical spacing in 19-inch rack-mount equipment.

### The inner can

The motherboard (plus any daughterboards) is accommodated in the inner can, a clamshell of folded sheet steel. This is a very rigid structure, on account of the folds in the metal and the boxsection formed by the baseplate and the motherboard. The sides of the motherboard protrude from the clamshell and engage with card guides in the outer case. The inner can provides mechanical protection and electrical and magnetic shielding.

## expansion

**Inner can** In an unexpanded Power1401-3A the clamshell comprises two pieces, the tray and the lid, with the motherboard clamped in between. Expanded units have a lid stretched to 2 U or 3 U, and an extender panel bolted onto the front face of the tray to raise its height to 2 U or 3 U.

The outer case The outer case of the Power1401-3A is built from 1-U aluminium extrusions. The side pieces have integral cardguides into which the inner-can assembly slides. The front and rear panels are bolted to the side pieces. The top and bottom plates are plastic-coated steel panels that slide into grooves in the side pieces and are retained by the font and rear panels. The screws securing the front panel are covered by the front-panel artwork sticker and consequently inaccessible in built units. Power1401s are supplied with lugs which bolt onto the outer case, for customers who wish to rack-mount their Power1401.

## expansion

Outer case Double- and triple-height outer cases are built from 1-U sections bolted together by 'stacker bars', which are metal spacers that fit between the side pieces. In each section, the front panel and side pieces are treated as a unit since the screws holding them together are hidden under the front-panel sticker. Expansion rear panels are blank. Assembling an expanded outer case involves screwing the front-and-side sections together with stacker bars, sliding-in the inner-can assembly and the top and bottom panels, then screwing-on the rear panels.

Earthing All metallic parts of the Power1401 enclosure are earthed. The inner can is tied to the earth rail of the circuit board via the screws that fix the board to the inner-can tray. The outer case is earthed by stout wires running from eyelets screwed to the outer-case metalwork to a spade tag connected to PCB earth. Expansion daughterboards are earthed via the brass spacer pillars. Earth continuity throughout the enclosure is ensured by metal-to-metal contact where parts are screwed together. There is a threaded M3 earth stud on the rear panel, for the earthing of auxiliary equipment. The Power1401 earth rail is connected to mains earth via the DC power socket and the earth leads of the power supply.

Upgrade by For most kinds of daughterboard it is feasible for a user to users expand a Power1401 in the field, though we do prefer units to be sent back to CED. No particular electronic expertise is required: the task should be well within the capability of an averagely practical person. Normal precautions against electrostatic discharge need to be taken. The expansion kit is quite economical since all parts of the unexpanded enclosure are reused apart from the inner-can lid. Detailed instructions are included in any expansion kit sent out to customers, as is a 2mm hex driver for the rear-panel screws. Opening a Power1401 is described on page 35.

Recalibration After a user has installed an expansion card in the field, it will be necessary to recalibrate the unit. Analogue gain is set by precision resistors at the time of manufacture and is not adjustable, but zeroing the offset to match the motherboard has to be done *in situ*. The user will have to run the calibration program, as described on page 41. This requires an accurate digital voltmeter (DVM) having a resolution of 10 µV on the ±5 V range.

## **Maintenance operations**

**Introduction** The Power1401 requires very little maintenance. This section covers simple operations that may occasionally need the case opened, such as setting the internal options switch, replacing damaged I/O chips, upgrading memory, or re-calibrating the analogue system. We also describe updating the flash ROM.

Taking the lid off To open the Power1401, turn the unit off and disconnect the power lead and any other cables. Unscrew the four M3 screws at the corners of the rear panel (or panels) with a 2 mm hex wrench. Do not unscrew the green & yellow earth wire. Slide out the top cover. Be careful not to splay the sides: the case loses rigidity once the back is off.

> The inner can is now visible. Slide it out to the rear, and unplug the green & yellow earth wire from the side. It may be quite tight. Undo the six M3 'combi' screws (with captive shakeproof washers) holding the lid on, using a 1-pt Pozidriv screwdriver. Gently pull the lid up and off. Note the position of the graphiteimpregnated gasket strips. They are quite delicate, so store them safely. The circuit board is now ready to be worked on.

To reassemble the Power1401, simply reverse this procedure.

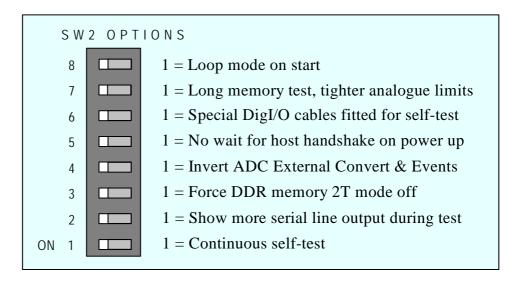

Switch settings This diagram shows the internal options switch settings on the Power1401. Logically, On counts as 0, Off as 1. Most options concern self-test and debug. Normally, all switches must be On, physically towards the edge of the circuit board, as shown.

## I/O components

IC27, IC28 & IC29 LM6511IM/NoPb Evt1, Evt0 & Trig IC2 OPA2132UAE4 DAC1out & DAC0out

IC3, IC4 & IC5 SN74LVC1T45DRL CLK2, Dout1 & Dout0 IC8, IC11, IC13, IC15, IC17, IC19, IC21 & IC24 OPA827AIDGKT AnaIn7, AnaIn6, AnaIn5, AnaIn4, AnaIn3,

AnaIn2, AnaIn1 & AnaIn0

IC122 & IC123 SN74LVC8T245PW DigIn odd & DigIn even

IC93 & IC94 SN74LVC8T245PW DigOut 0-7 & DigOut 8-15

IC81 SN74LVC8T245PW RP Event input Top cluster:

IC99, IC100, IC101,

IC102, IC95, IC96 & IC97

SN74LVC1T45DRL

DRL, UserIn, DigOutDis,

DRH, NDRL, NDRH &

UserOut;

Bottom cluster:

IC124, IC125, IC126 &

IC127

SN74LVC1T45DRL

DAL, DAH, DTL & DTH

IC116, IC118 IC129, IC131, IC138, IC140, IC150 & IC151 OPA827AIDGKT AnaIn12, AnaIn10, AnaIn13, AnaIn11, AnaIn14, AnaIn8, AnaIn15 & AnaIn9

Memory The base-level Power1401-3A is supplied with 1 GByte of upgrades double data-rate synchronous dynamic RAM (DDR SDRAM). This is a dual in-line memory module (DIMM) in a socket. You can upgrade your memory to 2 GBytes simply by exchanging the DIMM. See page 35 on how to open a Power1401, and see the diagram on page 37 for the location of the socket. The Power1401 automatically detects the size of the installed memory at power-on, so there is usually no need to alter any switches or software settings if the memory is upgraded.

# specification

**Memory** Any memory you obtain should meet the following specification:

- DDR-2 SDRAM in 240-pin DIMM

- Speed: 800 MHz CL5 or CL6

- Standard: PC2-6400

DIMM memory not meeting this specification will not work. The CED warranty on the Power1401-3A does not cover malfunctions caused by users attempting to upgrade their units.

Suitable 2 GByte The Kingston KVR800D2N6/2G is a 2 GByte, non-ECC DDR memory DIMM DIMM that will run in the Power1401-3A.

**Self-test and** The standard, short self-test will take about 1 second. The long the memory test, which tests the memory, takes about 1 minute per gigabyte. To run it, position 7 of the internal options switch must be set, i.e. in the Off position (see page 35.)

**Testing** The long self-test must be run if you have fitted a 2 GByte 2 GByte DDR DDR. If it fails, the DAC and ADC LEDs will flash on and off at about 1 Hz. In this case, set position 3 of the internal options switch On, to enable 2T mode, and re-run the long test. If the DDR still fails, then that particular part is not usable.

Electrostatic When exchanging DIMMs, take precautions against static precautions electricity. Earth the Power1401 case to mains earth, and yourself to the case, preferably via a wrist strap. Release the old DIMM by pushing the small ejection levers on either side of the socket. Ensure the new DIMM has no static charge by touching its conductive wrapping before handling it. Avoid touching metallic contacts on the DIMM: it is best to hold it by the short edges. DIMMs are mechanically polarized: you cannot insert one upside down. Inserting the DIMM takes some force; the module is only truly inserted when the ejection levers snap shut.

Setting the ADC The ADC and DACs may together be set to a working range of input range ±5 V or ±10 V. This is done through TRY1401 (version 3.35 or later). The setting is stored in non-volatile memory and is not affected by power cycling. Your Power1401 will be supplied with the default setting of  $\pm 5$  V unless you have asked for it to be supplied with the range set to  $\pm 10 \text{ V}$ .

Warning Note that analogue performance is inherently poorer on the ±10 V range: ADC inter-channel cross-talk rises disproportionately faster with sampling rate, and DAC settling time is longer.

To alter the voltage range, select

Start, All Programs, 1401 support, TRY1401

Inside the File menu, click on 1401 Options... Select from the dropdown list to set the ADC and DACs working range. Hit OK to confirm the change, or Cancel, as appropriate. The change takes effect the next time the Power1401 is power-cycled.

# Power1401-3A **Monitor**

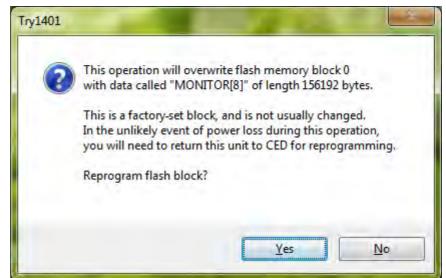

Flash ROM The Power1401 stores various software items in its non-volatile and the SPI flash ROM. The primary boot loader, the power-on self-test firmware, and the monitor (the operating firmware) are all stored in block 0. The FPGA configuration image is stored in block 1. Both blocks are automatically loaded on power-up, so long as the rear-panel Mode selector is in position 1. This tells the primary boot loader to load blocks 0 and 1.

### Memory block overwrite warning

Upgrades and Monitor and FPGA upgrades are available as .fli files from the Internet the Downloads page of CED's website, www.ced.co.uk. You will find detailed instructions there on downloading the files.

**TRY1401** Monitor and FPGA upgrades are implemented by updating the SPI flash ROM using the TRY1401 utility. To open TRY1401, select

Start, All Programs, 1401 support, TRY1401

From File select Update Flash. The destination for the new monitor is set automatically to block 2, and the FPGA image to block 3, so the old monitor and FPGA images are still there in case of disaster, e.g. power failure during the few seconds taken writing the file. Blocks 0 and 1 are pre-loaded. If you do write to them you are warned first. To use the new monitor or FPGA image, set the rear-panel Mode selector to 2 and switch the Power1401 DC off and on again. Check that the Power1401 is operating correctly.

Analogue The ADC & DAC Test option inside TRY1401 is provided to calibration calibrate the ADC inputs. Before we ship your unit, we run this program and set the waveform system to an accuracy of approximately 0.5 mV, or three least significant bits (LSBs). On the ±5 V range, one sixteen-bit LSB corresponds to only 150 µV, which is of the same magnitude as the drift caused by the normal ageing of components. Therefore, if accurate voltage measurement is important to you, we suggest that you calibrate your Power1401 against a known standard as part of your experimental protocols, and check the absolute accuracy once every six months. We find that most units drift by substantially less than thirty-two LSBs (0.05%) over this period.

**Equipment needed** To make use of this program you will need two BNC-to-BNC cables, a BNC tee-junction, and an accurate digital voltmeter (DVM) having a resolution of 10 μV on the ±5 V range. It is most important that you allow the Power1401 to warm up, with power on for at least thirty minutes before you start the calibration, to allow the system to reach thermal equilibrium.

> Alternatively, you may choose to return your Power1401 to CED for calibration. See page 45 for advice on sending it back.

Running TRY1401 To run TRY1401, select

Start, All Programs, 1401 support, TRY1401

ADC & DAC Test is an option inside Tests. The screen instructions detail the equipment required and the actions taken at each step. The procedure involves calibrating the DACs against the DVM, then calibrating the ADC against DAC0.

## precautions

**Electrostatic** When working inside the Power1401 take precautions against static electricity. The case is connected to mains earth via the power cable. Earth yourself to the case, preferably via a wrist strap.

# Power1401

Cleaning the The Power1401 needs periodical cleaning to remain in good condition. Before cleaning, remove power and all cables from the Power1401.

> The exteriors of the Power1401 case and the power supply should be cleaned annually to remove deposits of foreign matter, with a soft cloth moistened with a mild detergent solution. Avoid spilling drops of water or any other liquid on the Power1401. Note: this product is not designed to withstand aggressive or caustic cleansing products, nor is it proof against ingress of liquids.

> Check the BNC connectors and rear-panel plugs and sockets for pieces of paper or fluff. If any are seen, remove them with a pin.

Check cables visually for fraying or other mechanical damage.

## **Trouble shooting**

**Overview** The Power1401 has comprehensive built-in self-test capabilities which are backed up by a range of test and diagnostic programs to help pin-point problems quickly. If you suspect that you have a hardware fault, you should follow the procedures below to obtain as much information as you can about the problem, then call the CED Hardware Help Desk for advice.

Stand-alone test This is the simplest test of a Power1401. It eliminates the possibility of a host computer or cable fault confusing the situation. Disconnect the Power1401 from the host at the 1401 end of the USB cable, remove all signal connections and then apply power to the Power1401.

Power-on self-test The  $\circlearrowleft$  indicator should switch on glowing red. The firmware first performs a short memory test, then tests the rest of the hardware. During this time, the ADC and DAC LEDs dance in characteristic patterns. If all is well, the  $oldsymbol{\circlearrowleft}$  indicator then turns green. The yellow LEDs continue to flicker, only stopping when the Power1401 is reconnected to a working computer.

### U indicator flashing red and green

If the **U** indicator flashes red and green at the end of the powerup self-test, the Power1401 self-test firmware has detected a problem. It is likely that TRY1401 will be able to provide details of the problem. You will need to connect your Power1401 to the host computer before running the test. Open TRY1401 by selecting

Start, All Programs, 1401 support, TRY1401

### **Running TRY1401**

Check the Self test box, then click on Run once. If no errors are detected it may be worth running continuous self-test (Run cont) to pick up any intermittent fault. Inform CED of any reported errors: File, Send Mail will create a new email with the report as an attachment (you can also copy and paste.) Our hardware help address is hardhelp@ced.co.uk.

**LED diagnostic** The self-diagnostic firmware of the Power1401-3A can display patterns a number of patterns on the front-panel BNC LEDs and the U indicator. These indicate normal running, the phases of selftest, and various error conditions.

What is seen In the table below, the yellow LEDs referred-to are the two DACs and the eight ADC inputs. The state of the six LEDs on the right is not relevant. Behaviour is as below:

- Bar graph: LEDs light progressively from left to right (memory write), then retreat (memory read)

- Test numbers: LEDs show the test number, LSB on the *left*

- Frozen pattern: LEDs halt on the number of the failed test

- Binary ramp: LEDs count up in binary, LSB on *left*

- Dancing DACs: the two leftmost LEDs toggle their original states at 1 Hz

- As per program / As before: LEDs continue doing whatever they were doing before

| 1401 status               | Yellow LEDs    | <b>ს</b> Indicator |

|---------------------------|----------------|--------------------|

| Normal running            | As per program | Green              |

| Memory test               | Bar graph      | Red                |

| Memory test fail          | All flashing   | Red                |

| Self-test                 | Test numbers   | Red                |

| Self-test fail            | Frozen pattern | Flashing red/green |

| Self-test pass, cable out | Binary ramp    | Green              |

| Self-test pass, cable in  | All off        | Green              |

| Total hardware failure    | All on         | Red                |

| CPU crash                 | Dancing DACs   | As before          |

| Software error            | As per program | Red                |

| Over-temperature          | All on         | Off                |

Calling the If you cannot diagnose your Power1401 problems yourself, do CED Help Desk call our Hardware Help Desk. Please email if possible. Our email address is:

hardhelp@ced.co.uk

We also have a direct phone line to the Hardware Help Desk:

+44 (0)1223 433477

Otherwise, our phone and fax numbers are at the front of this manual. If your email has attached files, please ensure that they are less than 1 MByte (zipped). To save yourself time, and improve the efficiency of the process:

- Please find the serial number of your machine, printed on the back, in the form P 6xxx.

- If the problem is with a program, please make a note of the version number, announced on entry, or from *Help, About...*.

- It is often useful for users to have run TRY1401, so that we know about the hardware state.

### **Sending it back** If you need to send the Power1401 back to CED:

- You must first get a returns number from CED.